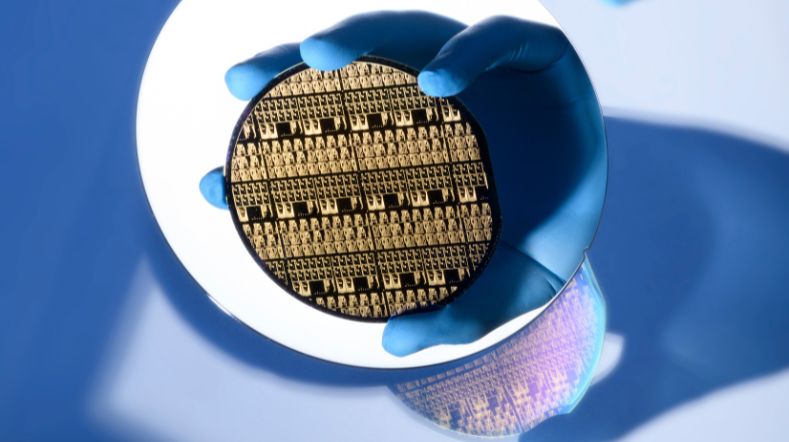

Built to move photonic-chip fabrication toward efficient industrial throughput.

Design InP Chips at the speed of light.

Aitonomi Photonics automates the development of InP photonic chips, helping teams generate, simulate, optimize, and prepare manufacturable indium phosphide photonic integrated circuits with physics-aware AI and foundry-conscious constraints.

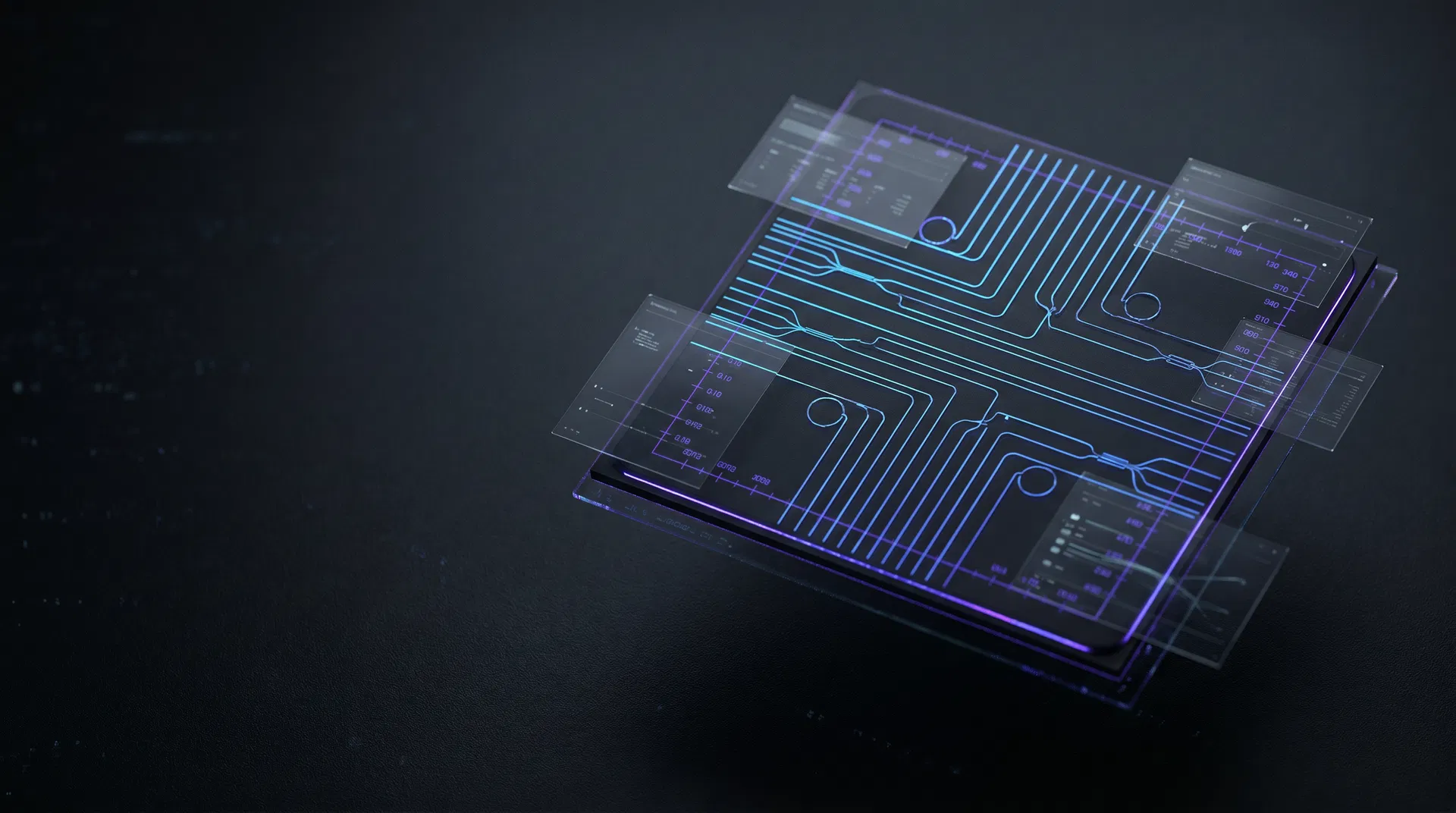

A new 6-inch InP manufacturing path is taking shape at High Tech Campus Eindhoven.

TNO’s PIXEurope pilot line connects research and industrial manufacturing for advanced indium phosphide photonic chips, giving design teams a European route from AI-assisted topology to realistic fab validation.

Building and cleanroom infrastructure are being constructed at High Tech Campus Eindhoven.

Part of Europe’s open-access initiative for photonic chips under the Chips JU ecosystem.

Reported target for the facility as it scales toward industrial manufacturing capacity.

Sources: TNO and PhotonDelta

A world-first co-pilot for difficult InP photonic decisions.

Replace disconnected scripts, late-stage simulations, and intuition-only tradeoffs with a world-first unified design environment built for InP photonic integrated circuits.

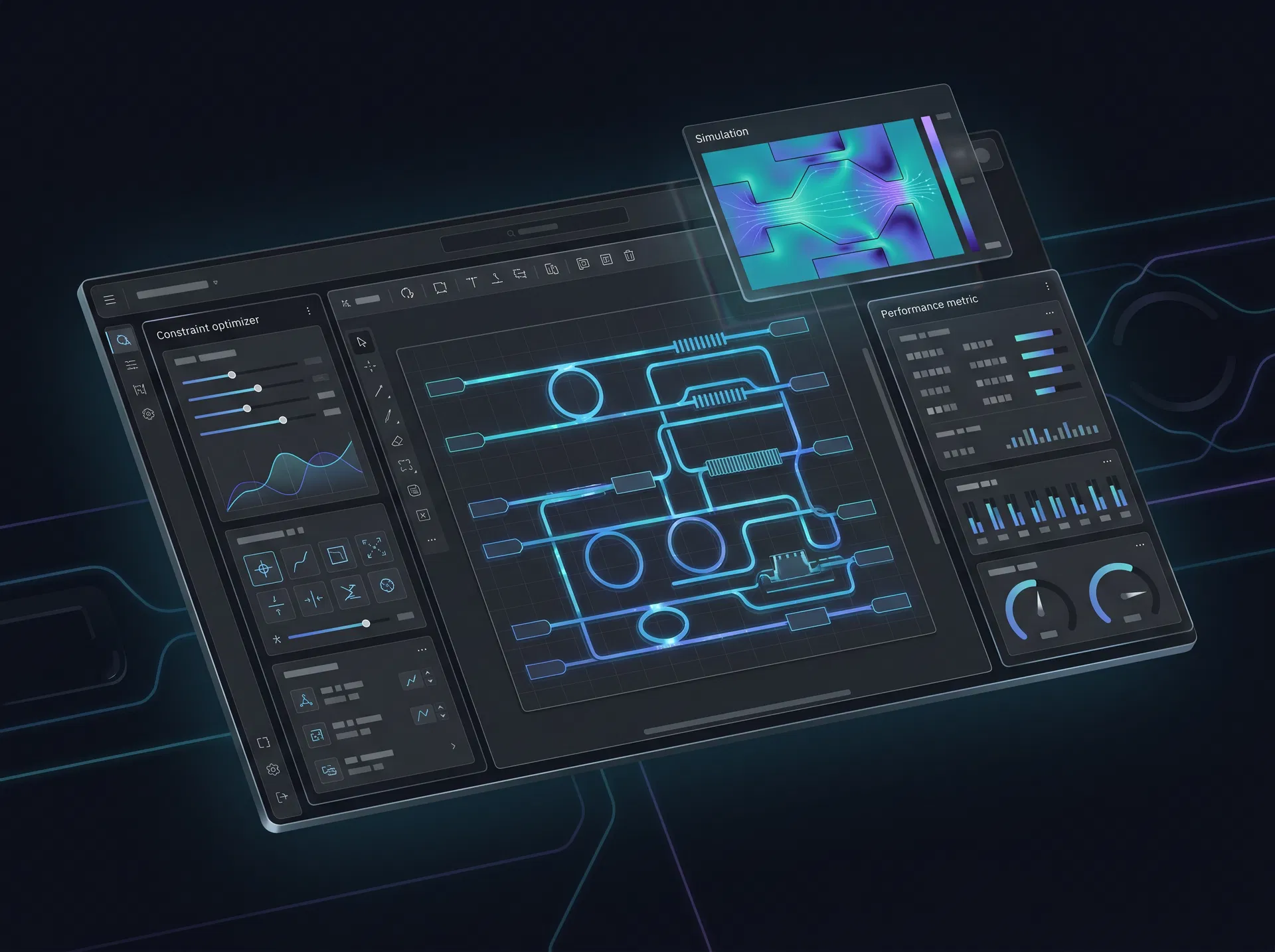

Generate InP photonic layouts from system intent.

Explore InP waveguide networks, resonator configurations, splitter trees, and active/passive component choices against manufacturable design rules before committing engineering weeks.

Keep electromagnetic behavior inside the design loop.

Surrogate models, field solvers, and compact-model feedback help teams compare performance, loss, thermal drift, and process variation earlier.

Move from concept to verified masks without translation loss.

Constraint libraries, versioned experiments, and export-ready layouts support InP photonics design flows and foundry collaboration.

One environment from topology to InP tapeout packet.

Engineers can compare generated architectures, inspect constraint pressure, trigger simulation tiers, and preserve design rationale without leaving the platform.

From Düsseldorf campus energy to chip-design laboratory discipline.

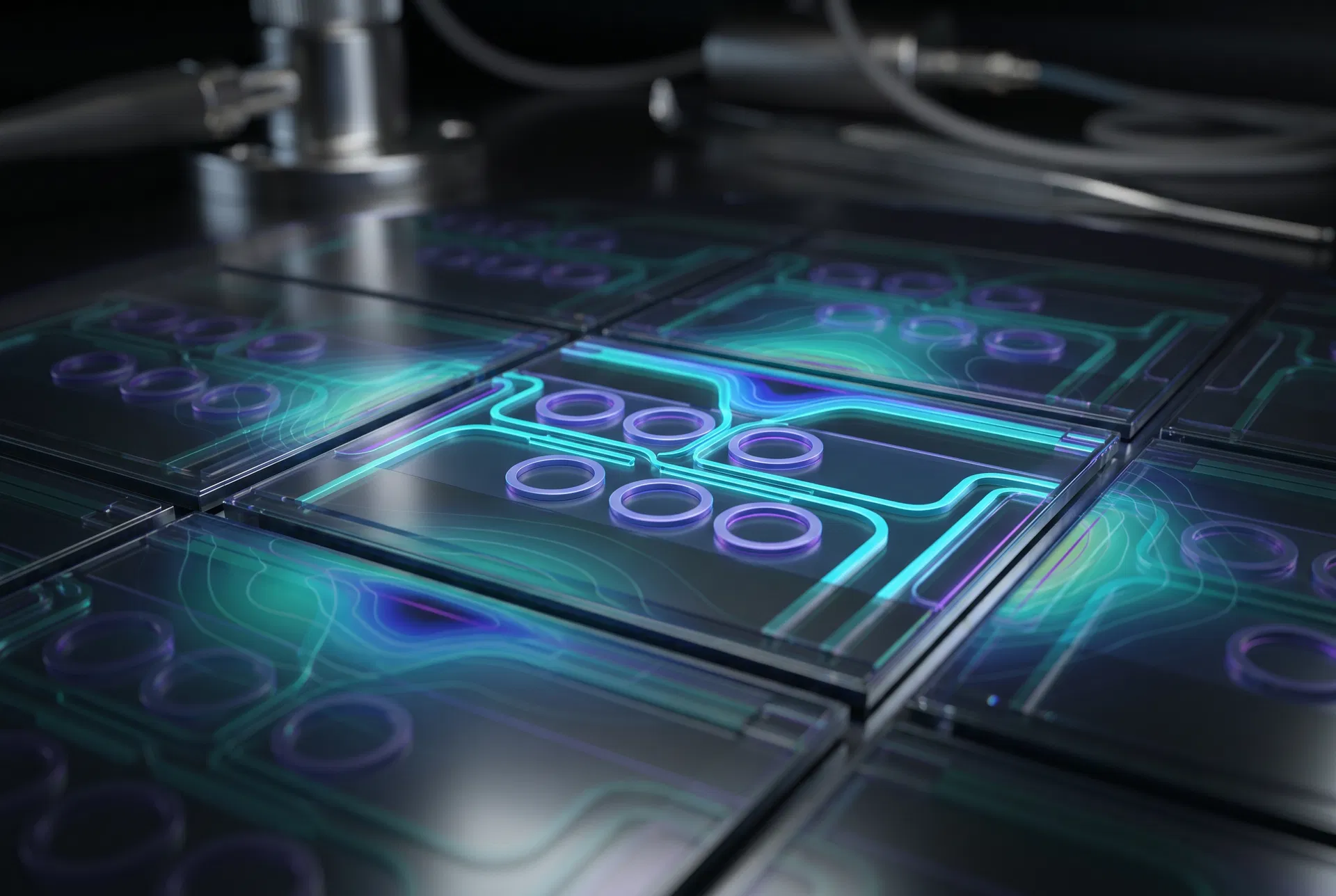

The visual system connects Aitonomi Photonics to a European deep-tech environment: TRIO campus imagery signals proximity to Düsseldorf's innovation ecosystem, while the laboratory scene grounds the world-first InP photonic chip developments in design verification, wafer review, and multidisciplinary engineering.

Software that respects experimental reality.

A stronger laboratory story shows the bridge between world-first AI-generated InP photonic architectures and the scientists who validate optical performance, process assumptions, and manufacturing readiness.

A European base for photonics collaboration.

Campus visuals add a grounded sense of place for partners, investors, and technical teams evaluating Aitonomi Photonics from the DACH innovation corridor.

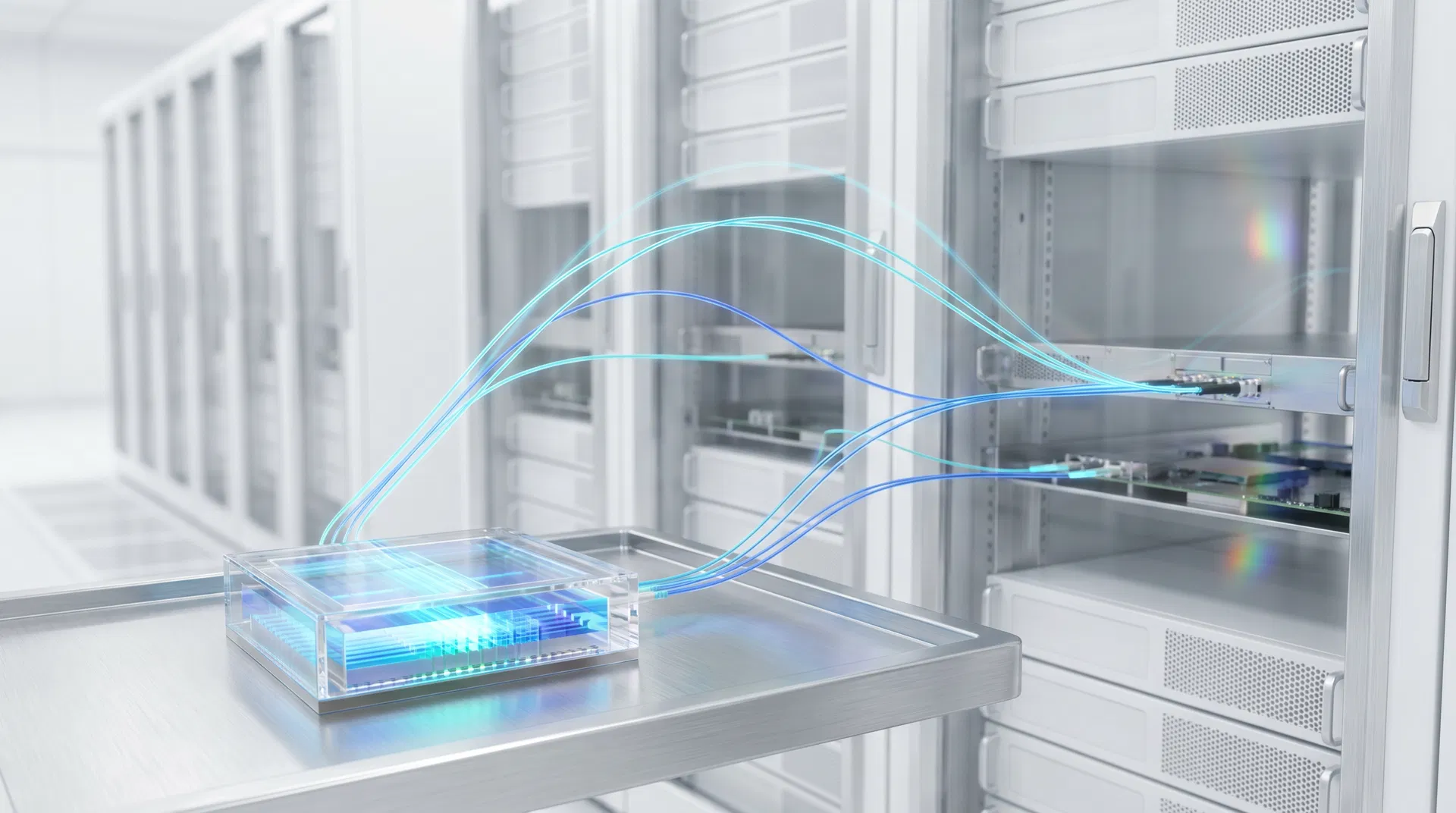

InP photonics for data centers and autonomous driving.

Aitonomi Group connects InP photonic-chip design to two high-value AI infrastructure use cases: optical data-center connectivity for accelerator clusters and autonomous-driving systems that depend on fast sensing, fusion, and efficient edge intelligence.

Move bandwidth with light inside AI clusters.

InP photonic circuits can support optical interconnects, co-packaged optics, and low-latency links for dense accelerator systems where electrical I/O becomes a power and heat bottleneck.

Bring photonic sensing and efficient inference closer to the vehicle.

For autonomous-driving stacks, InP photonics can support LiDAR and coherent sensing paths, fast sensor fusion, and energy-aware edge inference for perception and control.

Application view: InP photonic chips link cloud-scale AI infrastructure with autonomy stacks that need high-bandwidth sensing and low-power intelligence.

Built for teams who cannot afford opaque automation.

Specify the optical system

Define wavelength bands, insertion-loss budgets, thermal limits, routing constraints, and preferred InP component families.

Search feasible architectures

AI agents evaluate candidate topologies while respecting InP waveguide bends, coupling gaps, footprint targets, and process assumptions.

Validate with model fidelity

Simulation tiers graduate from fast compact models to high-resolution field analysis where confidence and sensitivity demand it.

Package for manufacturing

Generate review packets, export layout-ready artifacts, and preserve the full reasoning chain for InP design reviews and foundry handoff.

Optimize for performance, manufacturability, and confidence.

Aitonomi Photonics is designed for organizations building world-first InP photonic chips where architecture choices affect downstream yield, packaging, and system economics.

Design-space intelligence

Rank candidates by optical loss, footprint, thermal stability, manufacturability, and architecture risk in one calibrated view.

Constraint-governed automation

Guardrails keep generated designs aligned with PDK limits, review policies, and team-specific engineering assumptions.

Yield-aware sensitivity

Surface performance cliffs, lithography tolerance concerns, and tuning margins before a topology becomes expensive to unwind.

Collaborative decision trails

Every experiment records inputs, model versions, comparisons, and tradeoff rationale for cross-functional design reviews.

Bring AI into the photonic design loop.

Use the form brief below to frame a technical review for your team. As part of the Aitonomi Group technology narrative, Aitonomi Photonics is positioned for world-first InP photonic chip developments across startups, semiconductor groups, foundries, and infrastructure teams designing high-bandwidth optical systems.